БЛОКИ ПИТАНИЯ ЦИФРОВЫХ УСТРОЙСТВ

Цифровые устройства, собираемые радиолюбителями на микросхемах серии KJ55, требуют напряжения питания 5 В при токах от долей ампера до единиц ампер. Блоки питания таких устройств обычно собирают по тра« диционной схеме трансформатор — диодный мост — емкостный фильтр — стабилизатор. Схема одного из вариантов блока питания, пригодного для всех они» санных выше устройств на ИС серии КД55, приведена на рис. 87.

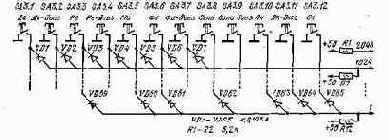

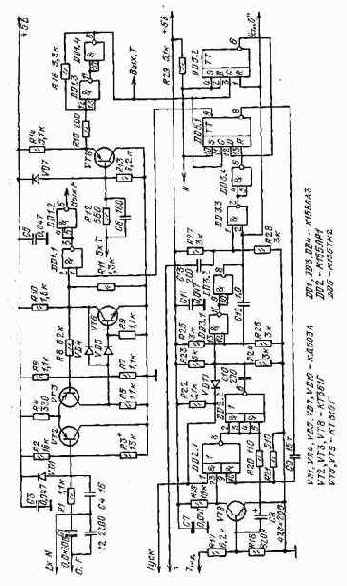

Рис. 87. Схема блока питания с низкочастотным трансформатором

Трансформатор 77 намотан на магнитопроводе ШЛ16Х25, обмотка I содержит 1900 витков провода ПЭВ-1 диаметром 0,15 мм, II — 90 витков ПЭВ-2 диаметром 0,64 мм, III — 270 витков ПЭВ-1 диаметром 0,15 мм, IV — 22 витка того же провода, V — 2000 витков провода 0,1 мм. Естественно, что нужно намотать лишь необходимые для питания данного устройства обмотки. Транзистор VT7 необходимо установить на радиатор.

При наличии микросхемы К142ЕН1 с любым буквенным индексом стабилизатор можно собрать по схеме рис. 72.

Блоки питания с низкочастотным трансформатором имеют значительные габариты и массу, нередко существенно превосходящие габариты и массу самих устройств.

Использование высоковольтных транзисторов серий КТ604, КТ605, КТ704, КТ809, КТ824 позволяет строить блоки питания с преобразованием напряжения на высокой частоте, имеющие меньшие массу и габариты, чем собранные по традиционной схеме.

Такие блоки питания строятся по схеме выпрямитель напряжения сети — емкостный фильтр — преобразователь постоянного напряжения в переменное с частотой 20 — 40 кГц с понижающим трансформатором на ферритовом кольцевом магнитопроводе выпрямитель — фильтр и, при необходимости, стабилизатор.

Ниже описаны два блока питания цифровых устройств. Первый из них обеспечивает выходное нестабилизированное напряжение около 5 В при токе нагрузки до 0,8 А и предназначен для питания, электронных часов и цифрового таймера. Второй обеспечивает стабилизированные напряжения +5 В 1 А, + 12,6 В и — 12,6 В 100 мА и нестабилизированное напряжение +2О0 В 10 мА и может быть использован для питания цифрового частотомера или мультиметра.

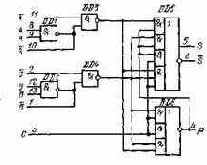

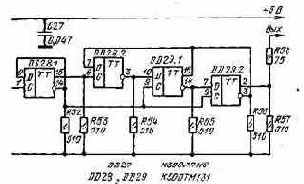

Рис. 88. Полумостовой преобразователь

В основе обоих блоков питания лежит так называемый полумостовой преобразователь напряжения (рис. 88). Первичная обмотка трансформатора преобразователя включена в диагональ моста, образованного двумя последовательно включенными транзисторами и двумя конденсаторами. В отличие от обычно используемой в преобразователях с низким входным напряжением схеме, в которой полное входное напряжение поочередно подается к двум половинам первичной обмотки, в полумостовом преобразователе ко всей первичной обмотке прикладывается половина напряжения питания, в результате чего число витков первичной обмотки можно сделать в 4 раза меньшим. Более важным преимуществом полу-мостового преобразователя перед упомянутой схемой является вдвое меньшее напряжение, прикладываемое к транзисторам. Это напряжение в полумостовом преобразователе равно напряжению питания (около 300 В при напряжении сети 220 В), тогда как в обычно используемой схеме — удвоенному напряжению питания.

В преобразователях напряжения мощностью в сотни ватт используются также мостовые схемы, в которых первичная обмотка трансформатора включена в диагональ моста из четырех транзисторов, но такие преобразователи заметно сложнее полумостовых.

Рассмотрим схему первого блока питания (рис. 89). Сетевое напряжение выпрямляется мостом VD1, пульсации сглаживаются конденсатором СЗ. Мост преобразователя образован конденсаторами С4, С5 и транзисторами VT6 — VT9. Для обеспечения необходимой выходной мощности в каждое плечо включено параллельно по два транзистора типа КТ605А.

Рис. 89. Схема блока питания для таймера или электронных часов

Преобразователь имеет специальную цепь запуска, собранную на транзисторе VT10 и элементах С12, R8 — R10. Транзистор VT10 типа КТ315Б работает в лавинном режиме. После включения питания конденсатор С12 заряжается через резистор R8. Когда напряжение на коллекторе VT10 достигает 40 — 60 В, он лавинообразно включается и конденсатор С12 разряжается.

Ток разряда ограничен резистором R10, длительность определяется постоянной времени C12R10.

Импульс тока включает транзистор и запускает преобразователь. Отрицательные полупериоды напряжения с базы VT9 прикладываются к эмиттеру VTIO и периодически включают этот транзистор. В результате конденсатор С12 поддерживается в разряженном состоянии и колебаний в цепи запуска больше не возникает. Если по какой-либо причине колебания в преобразователе сорвутся, конденсатор С12 вновь начнет заряжаться, цепь запуска вновь выдаст импульс и преобразователь запустится.

Напряжение с двух половин вторичной обмотки выпрямляется диодами VD4, VD5, пульсации сглаживаются конденсаторами С6 и С7. Амплитуда пульсаций от пика до пика на выходе блока питания составляет около 0,3 В.

Ток, потребляемый блоком от сети, имеет вид коротких импульсов, заряжающих конденсатор СЗ. Этот ток, протекая через первичную обмотку трансформатора Т1, наводит во вторичной обмотке импульсы напряжения.

После ограничения стабилитроном. VD2 и фильтрации в цепи C1R2C2 импульсы поступают через эмиттерный повторитель на дополнительный выход блока и используются в таймере после деления до 11 Гц в качестве счетных импульсов. В электронных часах от блока питания не требуется выдачи импульсов с частотой сети, поэтому элементы цепи их формирования можно исключить, а резистор R1, ограничивающий бросок тока через VD1 при включении блока, необходимо увеличить до 36 Ом.

В блоке питания использованы конденсаторы типа К73-17 на рабочее напряжение 250 В (С4, С5), К50-29 (СЗ), КМ-6 (С1, С7), КМ-5а (С2, С8 — С12), резисторы типа МТ. Транзисторы КТ605А можно заменить на КТ604А. В качестве трансформатора Т1 использован импульсный трансформатор И49, имеющий две одинаковые обмотки с индуктивностью по 29 мГн. Такой трансформатор можно намотать на кольцевом магнитопроводе из феррита МЗООО типоразмера К10Х6Х5. Каждая из его обмоток должна содержать по 150 витков провода ПЭЛШО-0,12.

Трансформатор Т2 намотан на кольцевом магнитопроводе из феррита МЗООО типоразмера К32Х20Х6. Обмотка I содержит 150 витков провода ПЭЛШО-0,27, обмотка 11 — 2x6 витков ПЭВ-2 — 0,8 мм, III — IV — по 4 витка ПЭЛШО-0,27. Обмотки следует тщательно изолировать друг от друга, можно использовать для этой цели полиэтиленовую пленку. Обмотка I и каждая по-.ловина обмотки II должны быть равномерно распределены по окружности -кольца. При указанных параметрах трансформатора Т2 частота преобразования составляет около 30 кГц. Если трансформатор намотать на магнитоиро-воде из феррита М2000 типоразмера К28Х16Х9 с сохранением указанного числа витков, частота преобразования составит около 16 кГц.

Блок питания при аккуратном монтаже может быть собран в объеме гальванической батареи 3336. Налаживания блок не требует. Выходное напря-.жение блока должно составлять около 5 В при токе нагрузки 0,3 А и 4,8 В при 0,8 А. Если выходное напряжение отличается от указанных значений, необходимо подобрать число витков первичной обмотки Т2. Если преобразователь при включении не запускается, необходимо проверить осциллографом с закрытым входом напряжение на коллекторе VT10 — оно должно иметь вид пилообразных колебаний с частотой около нескольких сотен герц. Если колебания отсутствуют, необходимо заменить VT10.

Хорошей формы импульсов с частотой 50 Гц можно добиться, зашунти-ровав первичную обмотку Т1 резистором R* с сопротивлением несколько десятков омов, а также подобрав, при необходимости, емкость конденсаторов С1 и С2.

Однотрансформаторный преобразователь описанного блока имеет относительно низкий кпд — около 50%- Почти половина потребляемой от сети мощности рассеивается в трансформаторе Т2, магнитопровод которого работает в насыщенном режиме. Вторым и более серьезным недостатком однотрансфор-маторного преобразователя является наличие сквозных токов через транзисторы. Дело в том, что закрытые транзисторы начинают открываться одновременно с началом закрывания открытых транзисторов в момент насыщения трансформатора.

Открывание транзисторов происходит всегда быстрее, чем закрывание, в результате чего некоторое время (около 1 икс) транзисторы обоих плеч моста преобразователя оказываются включенными. Спасает транзисторы КТ605А от выхода их из строя относительно высокое сопротивление в со--стоянии насыщения. Попытка установить в однотрансформаторный преобразователь транзисторы с малым сопротивлением насыщения приводит к их быстрому выходу из строя.

Поэтому при требуемой во вторичной цепи мощности более 5 Вт более целесообразно применение двухтрансформаторных преобразователей, не имеющих указанных недостатков.

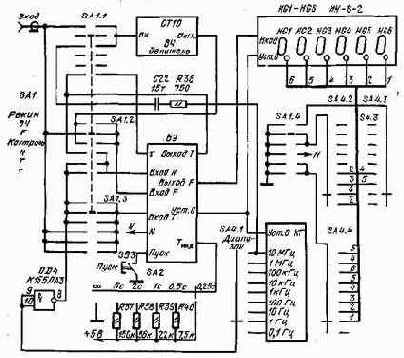

Схема блока питания с двухтрансформаторным преобразователем приведена на рис. 90. Первичная обмотка основного трансформатора преобразователя Т2 включена в диагональ моста, образованного транзисторами VT5, VT6 -и конденсаторами СЗ и С4.

Параметры трансформатора рассчитаны так, что его магнитопровод не входит в насыщение, поэтому потери в нем невелики. Базовые цепи транзисторов VT5 и VT6 получают питание от вторичных обмоток трансформатора Т1, магнитопровод которого может входить в насыщение, однако из-за малых размеров магнитопровода потери в нем относительно малы.

Отсутствие сквозных токов через транзисторы преобразователя объясняется следующим. Ток базы включенного транзистора уменьшается во времени за счет увеличения тока намагничивания трансформатора VT1. Когда ток базы станет меньше необходимого для поддержания транзистора в насыщенном состоянии, транзистор начнет выключаться, но лишь после прекращения тока j через него напряжение на первичной обмотке Т2 начнет изменяться, и только в результате этого начнет включаться транзистор второго плеча преобразователя. Таким образом транзисторы двухтрансформаторного преобразователя не бывают включенными одновременно, что исключает появление сквозных токов. Однако это верно лишь в том случае, если основной трансформатор преобразователя не входит в режим насыщения.

Если же трансформаторы рассчитаны неправильно и трансформатор Т2 входит в насыщение раньше, чем ток базы уменьшается до нуля, появляются сквозные токи транзисторов VT5 и VT6 и они выходят из строя.

Рис. 90. Схема блока питания для частотомера или мультиметра

Использование довольно мощных диодов в выпрямителе сетевого напряжения объясняется необходимостью для уменьшения потерь до предела снизить номинальное значение ограничительного резистора R1. Дроссели L1 и L2 уменьшают проникновение высокочастотных помех от преобразователя в сеть. Резистор R7 разряжает СЗ и облегчает запуск преобразователя при повторных включениях. Подстройкой резистора R6 можно в широких пределах менять частоту работы преобразователя.

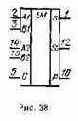

Блок питания собран на печатной плате размером 155x80 мм из двустороннего фольгированного стеклотекстолита толщиной 1,5 мм.

На стороне установки элементов фольга сохранена полностью и выполняет роль общего провода и экрана. Расположение проводников на противоположной стороне показано на рис. 91. Отверстия, кроме помеченных на рис. 91 дрестиками, означающими пайку к фольге общего провода, на стороне установки элементов раззенкованы. Диоды VD1 — VD4, транзисторы VT5, VT6 и подстроечный резистор R6 укреплены на небольших платах из двустороннего стеклотекстолита, подпаянных перпендикулярно к фольге общего провода. Высота плат 27 мм.

Для подключения к устройству, в котором используется блок питания, в печатную плату впаяны штырьки диаметром 1 мм от разъема ШР. Два штырька, обозначенные на рис. 90 и 91 буквой I, предназначены для контроля тока, потребляемого преобразователем при настройке (после настройки между ними устанавливается перемычка), штырек F — для контроля частоты.

Интегральная микросхема DA3 установлена в окне печатной платы, она закреплена двумя винтами JVL2.5 на радиаторе, который, в свою очередь, крепится вплотную к печатной плате. Радиатор игольчатый, с размерами 40X Х40Х27 мм.

В блоке питания использованы резисторы МТ, конденсаторы К.50-29 (С1, С2), К73-17 (СЗ, С4, С6), КМ-5а (С5, С9, С13), КМ-6 (С7, С8, СИ, CJ2, С14 — С19), стандартные дроссели Д-1,0 (LI, L2), ДМ-0,1 (L3 — L5), ДМ-2,4 (L6). Подстроечный резистор R6 типа СП5-16ВБ-0.5 Вт.

Транзисторы VT5 и VT6 должны иметь близкие коэффициенты усиления, их можно заменить на КТ704, КТ812, КТ824 с любым буквенным индексом, К.Т809А. Выпрямитель VD10 можно собрать из четырех диодов КД104А, а вместо диодов VD11 — VD18 использовать КД509А или сборки КЦ407А, КД906Л, К142НД1, К142НД4, К142НД5. Диоды КД213А можно заменить на КД213Б или КД212А.

Трансформатор 77 намотан на кольцевом магнитопроводе из феррита M3000 типоразмера К10Х6Х5. Первичная обмотка содержит 30 витков, вторичные — по 6 витков провода ПЭЛШО-0,27. Трансформатор Т2 намотан на кольцевом магнитопроводе М2000 типоразмера К28Х16Х9. Обмотка I содержит 110 вит--ков провода ПЭЛШО-0,27, обмотка II — 160 витков ПЭЛШО-0,1, III и IV — по 16 витков ПЭЛШО-0,27, V — 2X8 витков ПЭВ-2-1,0. Витки обмоток следует равномерно распределить по магнитопроводу (для обмотки V — каждую половину).

Для настройки к контактам I следует подключить миллиамперметр на 100 мА, к выходу стабилизатора 5 В — резистор 5 Ом 5 Вт, к контакту F и общему проводу — частотомер и (или) осциллограф.

Резистор Д6 следует установить в положение максимального сопротивления, после чего включить блок питания. После возникновения генерации необходимо сразу же измерить ее частоту и, если она менее 20 кГц, сразу же отключить блок от сети. Если частота превышает 20 кГц, ее следует уменьшить, плавно вращая ось резистора R6. При уменьшении частоты ток потребления, измеряемый прибором (примерно 45 мА), незначительно увеличивается, однако при частоте около 20 кГц начинается резкое возрастание тока, что указывает на переход трансформатора преобразователя в насыщенный режим р появление сквозных токов транзисторов. Частоту преобразователя целесообразно установить примерно в 2 раза большей частоты, при которой происходит резкое увеличение потребляемого тока. Хотя при несколько большей частоте ток потребления снижается, увеличивать ее не следует из-за ухудшения условия возбуждения преобразователя.

Рис. 91. Печатная плата блока питания

Если подстройкой R6 нельзя установить необходимой частоты, можно изменить число витков Т1, сохранив коэффициент трансформации. Для снижения частоты необходимо увеличить число витков, для увеличения — уменьшить.

Подключив к выходам ±12,6 В резисторы с сопротивлением 120 — 150 Ом 2 Вт, следует подобрать резисторы R8-R11 для получения необходимого выходного напряжения, при этом нельзя увеличивать R9 и JR.11 более 1,5 кОм.

Блок питания необходимо поместить в перфорированный латунный экран. Если прибор с таким блоком собран в металлическом корпусе, достаточно отделить его от остальных элементов прибора металлическим экраном или пластиной фольгированного стеклотекстолита.

Если стабилизатор напряжения собран по схеме рис. 90 с использованием микросхемы К142ЕН5А, стабилизатор напряжения в частотомере по схеме рис. 72 не нужен. При отсутствии микросхемы К.142ЕН5А следует сохранить фильтр C15C16L6C17C18, а стабилизатор собрать по схеме рис. 72.

ЦИФРОВАЯ ШКАЛА

Описываемое устройство может использоваться с трансивером или радиоприемником, частота которого определяется частотами одного, двух или трех генераторов.

Принцип работы шкалы в трансивере с тремя генераторами состоит в поочередном счете импульсов с частотой диапазонного F1, плавного F2 и опорного F3 генераторов в реверсивном счетчике за строго определенные периоды времени.

Рассмотрим в качестве примера широко распространенный вариант выбора частот гетеродинов, использованный в трансивере UW3DI: частота F1 в зависимости от диапазона лежит в пределах от 8 до 23 МГц, частота F2 изменяется в диапазоне 5,5 — 6,0 МГц, частота F3 составляет 500 кГц. При этом выходная частота составляет F=F1 + F2+F3 для диапазонов 28, 21 и 14 МГц и F = F1 — F2 — F3 для диапазонов 7 и 3,5 МГц.

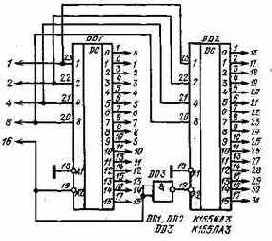

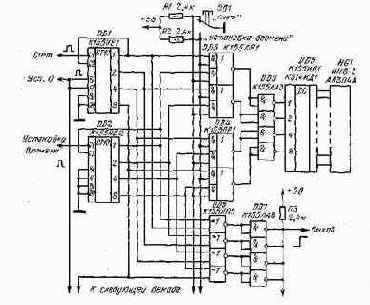

Рис. 75. Схема блока управления цифровой шкалы

Схема цифровой шкалы приведена на рис. 75 и 76. Измеряемые частоты поступают на входы Fl, F2, F3 и формируются в усилителях-ограничителях на транзисторах VT8, VT9, VT10. Их схемы идентичны, за исключением того, что емкость конденсатора, шунтирующего входной резистор в каналах F2 и F3, увеличена до 75 пФ. Частота F1 может превышать допустимую для интегральных микросхем К155ИЕ6, использованных в реверсивном счетчике, па-этому она предварительно делится на два триггером DD5.2 серии К131.

Рис. 76. Кварцевый reнератор и счетчик цифровой шкалы

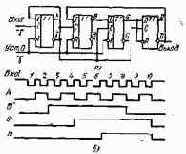

Сигнал эталонной частоты 1 МГц поступает на декадный делитель частоты DD1 — DD4 (см. рис. 75), с его выхода сигнал с частотой 100 Гц подается на вход формирователя временных интервалов, выполненного на ИС DD5.1, DD6, DD9, DD11 и элементах DD10.3, DD10.4. Работа формирователя иллюстрируется рис. 77. Импульсы с частотой 20 Гц поступают с выходов триггеров DD5.1, DD6.1, DD6.2 (см. рис. 75) на входы элементов DD9.1, DD9.2 и DD9.3, выполняющих функции дешифраторов и клапанов. Элемент DD9.1 пропускает один из каждых пяти импульсов последовательности ТИ2 с выхода 11 DD4. Эти импульсы устанавливают исходное состояние реверсивного счетчика.

Затем импульс В с выхода 6 DD6. 1 длительностью 20 мс, поступая на вход R триггера DD5.2, разрешает деление частоты F1 в этом триггере и частота F1/2 проходит через элементы DD10.3 и DD10.4 на вход сложения реверсивного счетчика.

Рис. 77. Диаграмма работы формирователя временных интервалов

Рис. 78. Диаграмма работы устройства динамической индикации

Элемент DD9.2 разрешает прохождение на реверсивный счетчик в тече» ние 10 мс импульсов с частотой F2, элемент DD9.2 — импульсов с частотоШ F3. Эти импульсы поступают на вход сложения или вычитания реверсивного счетчика в зависимости от логического уровня сигнала, поступающего на вход Управление шкалы. Если на входе Управление логический 0, то включен логический элемент DD11.3 и импульсы частот F2 и F3 проходят на вход сложения (диапазоны 14, 21, 28 МГц). Если на входе Управление 1, то включен DD11.1 и импульсы проходят на вход вычитания (диапазоны 3,5 и 7 МГц). Управляющий сигнал может определяться переключателем диапазонов тран-сивера — на диапазонах 28, 21 и 14 МГц вход управления должен быть соединен с общим проводом, на остальных оставлен свободным.

В результате в реверсивный счетчик записывается число, в 100 раз меньшее частоты трансивера, выраженной в герцах.

Коротким импульсом с выхода элемента DD10.2 производится перепись результата из счетчика DD15 — DD20 в сдвигающий регистр DD21 — DD26 (см. рис. 76). Индикация результата производится динамическим способом на вакуумном восьмиразрядном люминесцентном индикаторе HG1 типа ИВ-21. Работа элементов DD7, DD8, DD12, DD13 и транзисторов матриц VT11 — VT14, обеспечивающих динамический режим работы индикатора, иллюстрируется рис. 78. На входы элемента И — НЕ DD8.1 (см. рис. 75) подаются сигналы с частотами 100, 10, 5 и 1 кГц, в результате чего на выходе DD10.1 формируются пачки из четырех импульсов каждая, следующие друг за другом с частотой 1 кГц. Частота повторения импульсов внутри пачки — 100 кГц. Сформированные пачки подаются на вход сдвига сдвигающего регистра DD21 — DD26 (см.

рис. 76), замкнутого в кольцо. На выходах последних четырех разрядов сдвигающего регистра (DD26) последовательно формируются коды, соответствующие цифрам, которые необходимо индицировать. Коды цифр подаются через преобразователь двоично-десятичного кода в код семисегментного индикатора DD12 (см. рис. 75) и транзисторы транзисторных матриц VT11, VT12 — на соответствующие аноды индикатора HG1. Одновременно с каждой подачей пачки из четырех импульсов на счетный вход счетчика DD7 подается импульс, переключающий его в новое состояние. Выходы счетчика соединены со входами дешифратора DD13, выходы дешифратора через транзисторы матриц VT13, VT14 управляют сетками индикатора HG1. В результате в индикаторе поочередно зажигаются необходимые цифры.

После установки в 0 счетчика DD7, происходящей одновременно с переписью информации из реверсивного счетчика в сдвигающий регистр, на выходах DD26 формируется код цифры десятков мегагерц. Одновременно на сетку седьмой цифры индикатора ИВ-21 (счет цифр в нем ведется справа налево) подается положительное относительно катода напряжение, и загорается соответствующая цифра. Спустя 1 мс подается пачка импульсов, на выходе DD26 появляется код цифры единиц мегагерц, на сетку шестой цифры индикатора подается положительное напряжение и т. д. Одновременно с зажиганием шестой цифры положительное напряжение подается и на анод запятой, в результате чего на индикаторе цифры мегагерц от остальных цифр отделяются запятой.

Импульсы переписи информации имеют частоту 20 Гц, импульсы на сетках индикаторов — 167 Гц, в результате чего в каждом цикле измерения каждая цифра загорается 8 раз. Для исключения подсветки сегментов в моменты сдвига на вход гашения S преобразователя кода DD12 подаются гасящие импульсы с выхода DD8.2 с частотой 1 кГц.

Примененный способ динамической индикации по сравнению с использованием мультиплексеров требует меньшего количества ИС и значительно более прост в монтаже цепей.

Питание индикатора HG1 осуществляется от мостового выпрямителя на диодной матрице VD1 с конденсатором С1. Плюс выпрямленного напряжения соединен с плюсом источника 5 В, минус — через стабилитрон VD2 и диоды VD3, VD4 с катодом индикатора.

Диоды VD3 и VD4 образуют искусственную среднюю точку напряжения накала HG1, стабилитрон VD2 обеспечивает запирающее напряжение на сетках цифр, индикация которых в данный момент не производится.

В счетчике DD15 — DD20 (см. рис. 76), как указывалось выше, алгебраи-. чески суммируются результаты измерения трех частот. Из-за произвольного соотношения фаз измеряемых частот и эталонной частоты 1 МГц каждая из частот измеряется со случайной ошибкой в единицу младшего разряда. Полная ошибка может достигать трех единиц, причем величина ошибки для каждого цикла измерений случайна. В результате цифра сотен герц может хаотически изменяться 20 раз в секунду.

Для уменьшения этого явления триггер DD5.2 устанавливается в фиксированное состояние перед началом счета частоты F1, что уменьшает неопределенность его начальной фазы. Кроме того, вход младшего разряда ИС DD21 соединен с общим проводом, в результате чего индицируемая цифра сотен герц всегда четная и диапазон хаотического изменения цифр сотен герц снижен до возможного минимума — одного знака. .

Конструктивно цифровая шкала выполнена на двух двусторонних печатных платах размером 85Xil30 мм из стеклотекстолита толщиной 1 мм.

На печатной плате с реверсивным счетчиком и сдвигающим регистром расположен также кварцевый генератор на ИС DD14. Платы соединены между собой четырьмя стойками высотой 22 мм. Выводы индикатора HG1 впаяны непосредственно в отверстия первой печатной платы, а сам индикатор установлен в промежутке между печатными платами. Вся конструкция помещена в алюминиевый корпус с габаритными размерами 33x135x90 мм. Верхняя и нижняя стенки корпуса имеют вентиляционные отверстия. Передняя стенка корпуса изготовлена из зеленого органического стекла.

К трансиверу шкала подключается через разъем РШ5-15ГВ, установленный на задней стенке корпуса. Для питания шкалы необходимы переменные напряжения 30 В 5 мА, 2,4 В 35 мА и стабилизированное постоянное напряжения 5 В 1 А. Обмотки трансформатора 30 В и 2,4 В должны быть изолированы между собой и от других цепей.

Напряжения измеряемых частот Fl, F2, F3 могут находиться в пределах 0,2 — 5 В.

Частота кварцевого генератора может быть кратной 100 кГц в пределах от 100 кГц до 1 МГц, 1,2 или 1,6 МГц. Для получения на выходе делителя частоты 100 кГц следует использовать микросхемы К155ИЕ2, К155ИЕ4 или К.155ИЕ5 в режиме соответствующего коэффициента деления частоты, соединив выводы ИС в соответствии с табл. 2.

Если в трансивере производится вычитание только одной частоты, выход 12 DD9.2 следует подключить к дополнительному входу DD10.3, в качестве которого необходимо установить трехвходовой элемент И — НЕ, а выходы 1 и 2 DD11.4 объединить. При таком изменении частота F2 всегда будет подаваться только на вход сложения.

При использовании шкалы в радиовещательном приемнике .вместо установки реверсивного счетчика перед началом счета в 0 необходима запись в счетчик числа, соответствующего промежуточной частоте. Если в приемнике один гетеродин, частота которого всегда выше принимаемой, а промежуточная частота 465 кГц, в счетчик необходимо записать число 99 535 кГц. В этом случае при подаче сигнала с частотой гетеродина на вход F1 будет происходить переполнение счетчика и на HG1 будет индицироваться частота приема.

Для предварительной записи в счетчик некоторого числа к общему проводу необходимо подключать только часть входов Dl — D8 микросхем счетчика. При промежуточной частоте 465 кГц необходимо записать число 99 535 кГц, для чего у ИС DD20 и DD19 соединить с общим проводом входы D2 и D4 (запись числа 9), у DD18 и DD16 — входы D2 и D8 (число 5), у DD17 — входы D4 и D8 (число 3), у DD15 — все входы D (число 0).

Поскольку при одном гетеродине входы F2 и F3 не нужны, элементы усилителей-ограничителей этих каналов можно не устанавливать, а выводы 1 и 5 DD9 соединить с общим проводом.

При отсутствии микросхемы К514ИД1 вместо нее можно использовать К514ИД2, включив транзисторы матриц VT11 и VT12 аналогично транзисторам VT13 и VT14, дополнительно установив между базами транзисторов и выходами микросхемы К514ИД2 резисторы с сопротивлением 1,5 кОм.

Интегральные микросхемы серии К155 можно заменить аналогичными ИС серии К133, ИС К131ТМ2 на К130ТМ2. В усилителях-ограничителях транзисторы КТ316А можно заменить на КТ316 с любыми буквенными индексами или другими импульсными транзисторами с временем рассасывания не более

15 не, диоды КД503А — любыми кремниевыми диодами. В качестве VDJ можно использовать любые диоды с рабочим напряжением не менее 50 В, в качестве VD2 любой стабилитрон на 6 — 10 В.

Индикатор ИВ-31 можно заменить на ИВ-18, увеличив напряжение накала до 5 В, или шестью любыми одноместными вакуумными люминесцентными индикаторами, установив соответствующее напряжение питания.

Рнс. 79. Схема устройства динамической индикации с использованием мультиплексеров

Транзисторные матрицы КТС622А можно заменить любыми кремниевыми р — n — р-транзи-сторами с допустимым напряжением коллектор — эмиттер не менее 40 В.

При отсутствии ошибок в исправных деталях в шкале при настройке необходимо лишь установить точно частоту кварцевого генератора подбором емкости кон- денсаторов С14 и С15. Если даже при замене С15 перемычкой частоту генератора не удается снизить до необходимой, можно на место» С15 установить дроссель с индуктивностью 5 — 20 мкГн.

На рис. 79 приведен вариант-схемы динамической индикации с использованием мультиплексеров КЦ55КП7. В этом случае сдвигающий регистр заменяют статическим регистром на микросхемах К155ТМ5 или К155ТМ7, можно сохранить К155ИР1. Вместо сдвига используется опрос содержимого регистра памяти мультиплексерами DD27 — DD30. Микросхема DD8 и элемент-DD10.1 при этом не нужны, вход 5 DD12 надо оставить свободным.

Устройство динамической индикации с использованием мультиплексеров-.

сложнее устройства со сдвигающим регистром, если необходим промежуточный-регистр хранения информации. Если же такой регистр не требуется, например-при индикации показаний электронных часов, схема с мультиплексерами требует меньшего количества ИС. Поэтому в случае объединения цифровой шка- -лы и электронных часов, собранных, например, по схеме рис. 40, можно per комендовать схему динамической индикации с использованием мультиплексеров. В этом случае в качестве DD27 — DD30 (см. рис. 79) необходимо установить мультиплексеры К156КП1, в качестве DD13 — дешифратор К.155ИДЗ,. включив дополнительно между его выходами и базами двенадцати ключевых транзисторов резисторы сопротивлением 1,5 кОм. Счетчик DD7 должен работать в режиме деления на 12. Индикация должна осуществляться на двух. индикаторах ИВ-21 или ИВ-18, аноды которых объединены. Между выходами интегральных микросхем часов и входами мультиплексеров установки регистра памяти не требуется.

При использовании в качестве DD27 — DD30 интегральных микросхем К155КП1 или К155КП5, имеющих только инверсные выходы, необходимо между их выходами и входами DD12 включить инверторы, например одну микросхему К155ЛАЗ.

Фронты импульсов на выходах интегральных микросхем серии К155 имеют малую длительность, что является источником заметных помех во входном тракте трансивера или радиоприемника. Для исключения помех все цепи питания целесообразно вводить в корпус шкалы через Г-образные Z-C-фильтры с использованием дросселей на 20 — 100 мкГн и проходных конденсаторов емкостью 4700 пФ, необходим также хороший электрический контакт между корпусами шкалы и прибора, в который она встроена.

ГЕНЕРАТОР АККОРДОВ ДЛЯ ЭМИ

Описываемый генератор аккордов для электромузыкальных инструментов позволяет получать на выходе аккорды мажор, минор, септ-аккорд нажатием на одну клавишу. Схема генератора приведена на рис. 86.

Входы четырех мультиплексеров DD5 — DD8 подключены к выходам соответствующих делителей ЭМИ. Элементы DD1 — DD3 образуют шифратор кода 1 — 2 — 4 — 8. При нажатии на любую из кнопок переключателя SB1 на выходе шифратора образуется код, соответствующий нажатой кнопке. При нажатии, например, на кнопку SB1.7 (фа-диез) выключаются элементы DD2 и DD3-1 и на выходе шифратора появляется код 0110. Этот код поступает на адресные входы мультиплексеров DD5 и DD6, и на выходах появляются сигналы со входов 6 этих микросхем — фа-диез 1-й октавы и до-диез 2-й. На входы мультиплексеров DD7 и DD8 тот же код поступает через сумматоры DD9 в DD10. На вторые входы сумматора DD9 может также поступить код О0012=1ю при включении переключателя SA2.1 (мажор) или SA2.3 [септ-аккорд). На вторые входы DD10 при нажатии SA2.1 (мажор) или SA2.2 (ми-пор) поступит код 00102=2io. Эти коды в сумматорах складываются с кодом с выхода шифратора и, поступая на адресные входы DD7 и DD8, сдвигают номера входов микросхем DD7 и DD8, сигналы с которых поступают на их выходы.

Рис. 86. Схема генератора аккордов

Будем считать, для определенности, что включены SA2.1 nSA2.7. В этом случае на входах DD9 присутствуют коды 0110 и 0001, следовательно, на выходе DD9 код суммы — 01112=7ю. Этот код определяет прохождение на выход DD7 сигнала со входа 7 этой микросхемы — ля-диез 1-й октавы. Аналогично на входах DD10 коды ОНО и 0010, на выходе — 10002-810. На выход DD8 проходит сигнал со входа 8 этой микросхемы, т. е. фа-диез 2-й октавы. В результате в общей точке соединения резисторов R4 — R7 сформируется сложный сигнал, содержащий четыре частоты — фа-диез 1, ля-диез 1, до-диез 2, фа-диез 2, т. е. мажорный аккорд, взятый от ноты фа-диез 1-й октавы. Если включен SA2.2, то выходной сигнал содержит фа-диез 1, ля 1, до-диез 2, фа-диез 2, формируется минорный аккорд от фа-диез 1-й октавы.

При включении SA2. 3 выходной сигнал состоит из фа-диез 1, ля-диез 1, до-диез 2, ми 2 — септ-аккорд. Если нажимать другие кнопки переключателя SB1, будут формироваться указанные аккорды, но от других начальных нот первой октавы.

Для управления устройством формирования огибающей можно использовать сигнал с коллектора VT1. Если ни одна из кнопок SB1 не нажата, транзистор VT1 закрыт и на его коллекторе напряжение около +5 В. При нажатии любой из кнопок SB1 ток резистора R1 или входной ток микросхем-DD1 — DD3 включает VT1 и напряжение ОД — 0,2 В с его коллектора, поступая на вход управления УНЧ, включает формирователь огибающей.

Для того чтобы аккорды можно было брать не только от нот 1-й октавы, можно поступить так. Входы, подключаемые по схеме к выходам делителей 1-й октавы, подключить к соответствующим выходам 4-й октавы, подключаемые по схеме к выходам 2-й октавы — к выходам 5-й. Между выходами DD5 — DD8 и резисторами R4 — R7 включить четыре переключаемых делителя на двух микросхемах К155ИЕ5 каждый. В результате, оперируя тремя переключателями — SB1 Нота, SA2 — Аккорд и дополнительным переключателем Октава, можно будет взять любой аккорд от любой ноты ЭМИ.

На выходе сумматора схемы рис. 86 скважность импульсов каждой из частот, слагающих аккорд, соответствует скважности импульсов, поступающих на входы мультиплексеров. Если же формирователь дополнить делителями, как указано выше, скважность составляющих импульсов на выходе сумматора станет равной 2, если, конечно, не принять специальных мер.

Другим способом формирования аккордов может служить использование мультиплексеров на большее число входов. При таком способе скважность выходных импульсов будет равна скважности входных, однако схема формирователя и особенно его монтаж значительно усложняется.

При монтаже формирователя следует учесть, что в случае, если проводники, соединяющие контакты переключателей SB1 и SA2 с микросхемами DD1 и DD4, будут иметь длину более 100 — 200 мм, между этими проводниками и плюсом источника питания необходимо включить резисторы сопротивлением 5 — 10 кОм (аналогично R1), это исключит влияние помех на работу формирователя.

ГЕНЕРАТОР ДЛЯ НАСТРОЙКИ МУЗЫКАЛЬНЫХ ИНСТРУМЕНТОВ

Описываемый генератор позволяет получить на выходе сигнал с частотой, соответствующей любой ноте от контроктавы до пятой октавы.

Частота каждой ноты может быть установлена как точно в соответствии с хроматической гаммой, так и с поправкой до ±50 центов относительно этого значения, что позволяет настраивать инструменты по любой зависимости, в том числе и в соответствии с кривыми Мейнеля и Рейнсбека. Выбор частоты осуществляется тремя переключателями — Октава, Нота, Поправка. Дискретность установки частоты — 1 цент, ошибка в любой точке не превышает ±0,6 цента. Выходной сигнал генератора — меандр в уровнях ИС ТТЛ.

Схема генератора приведена на рис. 83. Задающий генератор собран на элементе DD1.1 и кварцевом резонаторе 11 на частоту 10 МГц. Через буферный каскад DD1.2 сигнал поступает на преобразователь частоты на интегральных микросхемах DD2 и DD3 типа К155ИЕ8. Выходная частота преобразователя в зависимости от сочетания сигналов, подаваемых на входы 1 — 32 DD2 и DD3, может составлять от 1/4096 до 4095/4096 входной частоты.

На входы 32 к 4 DD2 постоянно подан логический 0, логическая 1 — на входы 16, 8, 2, а также при показанном на схеме положении переключателя SAf.7 и на вход 1. При выключенных SA1.1 — SA1.6 на входы 1 — 32 DD3 также поступает уровень логического 0. В результате частота на выходе DD3 составляет (64+128 + 512+1024)/4096 = 1728/4096 от входной частоты. При включении SA1.6 коэффициент передачи DD2, DD3 увеличивается до (1728+1)/4096 от входной частоты. Относительное изменение выходной частоты составит 1729/1728=1,000 578 7, что очень близко к (2)-1200, т. е. к изменению частоты на 1 цент. Напомним, что относительное изменение частоты на один полутон составляет (2)-12, а на один цент — (2)-1200 . Включение переключателя SA1.5 увеличит частоту на 2 цента, SA1.4 — на 4 и т. д. Совместное включение нескольких переключателей увеличивает частоту на суммарную величину. В результате включением шести переключателей SA1.1 — SA1.6 можно увеличить частоту на 63 цента.

Если включить SA1. 7 при выключенных остальных переключателях, сигналы на входах 1 — 32 DD3 и на входе 1 DD2 изменятся на противоположные, суммарное изменение частоты составит 1+2 + 4 + 8+16+32 — 64= — 1 цент. Теперь включение SA1.6 будет уменьшать выходную частоту на 1 цент, включение SA1.5 — на 2 цента и т. д., т. е. включение SA1.7 изменяет знак воздействия SA1.1 — SA1.6. В результате соответствующим включением переключателей SA1.1 — SA1.7 выходную частоту преобразователя DD2, DD3 можно изменять на — 64- +63 цента. Указанная выше точность 0,6 цента выдерживается при введении поправки, не превышающей 50 центов.

Номинальная частота сигнала на выходе DD2, DD3 составляет 1728/4096Х Х10 МГц=4 218750 Гц. Этот сигнал через буферный инвертор поступает на вход еще одного преобразователя частоты на микросхемах DD4 и DD5. Управление коэффициентом передачи этого преобразователя осуществляется шифратором переключателя Нота. Каждой ноте соответствует определенный двоичный двенадцатиразрядный код, подаваемый на входы 1 — 32 DD4 — DJ5. Дли примера рассмотрим формирование сигнала с частотой ноты до. Для этой ноты код шифратора составляет 1000 0010 00012=208110. Коэффициент передачи делителя составит 2081/4096=0,508 066 64, а выходная номинальная частота преобразователя DD4, DD5 — 4 218 750X0,50 805 664=2 143 364 Гц.

Эта частота поступает на двоичный делитель на ИС. На выходе 12 DD8 частота уменьшится в 29 = 512 раз и составит 4186,26 Гц, что соответствует до 5-й октавы с точностью до 0,25 Гц. Ошибка в 0,25 Гц составляет 6-10-5 от точного значения, или приблизительно 0,1 цента.

Коды шифратора К для всех двенадцати нот приведены в табл. 4, там же указаны относительные отклонения Af/f получаемых частот от точного значения.

На других выходах ИС DD8, DD9 формируются частоты остальных октав, вплоть до контроктавы. Выбор нужной октавы осуществляется переключателем SA2. Схема соединения его контактов исключает замыкание выходов микросхем DD8, DD9 между собой при случайном включении двух кнопок.

Если в генератор установить кварцевый резонатор с частотой 5 МГц, на выходе 8 DD9 можно получать частоты субконтроктавы, а частоты 5-й октавы — на выходе 11 DD7. Такой же результат можно получить, добавив в схему генератора еще один счетный триггер между выходом 6 DD5 и входом 14 BD6.

Рис. 83. Генератор для настройки музыкальных инструментов

Таблица 4

Нетрудно видеть, что генератор вообще некритичен к исходной частоте. Практически возможно использование кварцевого резонатора на частоту от 1 до 15 МГц, необходимо лишь заново рассчитать коды шифратора ноты и соответственно изменить число двоичных делителей DD6 — DD9. Наиболее удобно использование кварцев с частотой от 9 592 200 Гц до 10 161000 Гц или с вдвое, или вчетверо, или в 8 раз более низкой частотой. Для них коэффициенты передачи преобразователя DD4, DD5, находятся в пределах приблизительно от 0,5 до 1, что обеспечивает максимальную точность формирования выходных частот.

При использовании кварцевых резонаторов с частотой менее 8 МГц может потребоваться изменение схемы кварцевого генератора.

Покажем, как рассчитать коды шифратора ноты для произвольной частоты кварца, превышающей 9 592 200 Гц. В табл. 4 приведены значения частот нот 5-й октавы, увеличенные в 29=512 раз, т. е. соответствующие выходной частоте преобразователя DD4, DD5 при частоте кварца, близкой к 10 МГц» Эти частоты следует разделить на номинальную выходную частоту преобразователя DD2, DD3, которая составляет 1728/4096 = 0,421 875 от частоты кварцевого генератора. В результате получится для каждой ноты коэффициент передачи преобразователя DD4, DD5, его следует умножить на 4096, округлить до ближайшего целого числа и перевести в двоичную форму.

Старший разряд двоичного эквивалента определит сигнал, который необходимо подать на вывод 3 DD4 (вход 2048), младший — на вывод 4 DD5 (вход 1). Если частота кварцевого резонатора близка к 10; 5; 2,5 или 1,25 МГц и находится в указанных выше пределах, все коэффициенты передачи, как-указывалось выше, заключены в интервале 0,5 — 1 и в старшем разряде двоичного эквивалента 1, что определяет подачу на вход 2048 логической единиц» независимо от ноты.

Если частота кварцевого резонатора ниже указанной, то ее перед расчетом следует умножить на 2, 4 или 8 так, чтобы она стала больше этого значения. Порядок расчета полностью сохраняется, а из схемы рис. 83 следует исключить соответственно 1, 2 или 3 разряда двоичного делителя.

Рис. 84. Схема шифратора для частоты кварцевого резонатора 10 МГц

По полученной таблице двоичных эквивалентов следует составить схему шифратора. Наиболее просто шифратор можно построить, используя переключатель П2К с взаимовыключением. Переключатель должен иметь 12 кнопок, каждая по 8 контактных групп на переключение. Если сгруппировать некоторые цепи шифратора, можно уменьшить число контактных групп. Схема шифратора для частоты кварцевого резонатора 10 МГц (естественно, пригодна» и для 5; 2,5; 1,25 МГц) приведена на рис. 84. Переключатель этого шифратора использует секции на четыре контактные группы.

При отсутствии переключателей с необходимым числом контактных групп Шифратор можно собрать на любых маломощных диодах. Необходимое число диодов соответствует общему числу нулей в двоичных эквивалентах коэффициентов передачи, для частоты кварца 10 МГц необходимо 65 диодов. Фрагмент схемы диодного шифратора приведен на рис. 85.

Рис. 85. Схема диодного шифратора

Переключатель SA1 — П2К с независимой фиксацией, SA2 — П2К с взаимовыключением (см. рис. 83).

Блок питания генератора должен обеспечивать напряжение 5 В при токе 0,6 А.

Настройка генератора сводится к точной установке частоты кварцевого генератора подбором С1 и, возможно, конденсатора, дополнительно включенного последовательно с кварцевым резонатором. Правильность формирования частот следует проверить с помощью цифрового частотомера. Контролировать частоты генератора целесообразно на выходе 6 DD5, они должны соответствовать указанным в табл. 4. Если отклонение частоты от необходимого значения превышает 0,025%, допущена ошибка в расчете или монтаже шифратора ноты.

Для настройки музыкальных инструментов не по хроматической гамме для каждой ноты следует вводить поправку, набирая ее на переключателе SA1. График или таблицу зависимости поправки от настраиваемой ноты целесообразно подложить под фальшпанель генератора, выполненную из органического стекла.

ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ КОМБИНАЦИОННОГО ТИПА

Среди ИС комбинационного типа наиболее широко используются дешифраторы, представленные в рассматриваемой серии микросхемами К165ИД1, К155ИДЗ и КЛ55ИД4.

Дешифратор К155ИДЗ (рис. 16) имеет четыре адресных входа 1, 2, 4, 8, два входа стробирования А1 и А2 и шестнадцать выходов 0 — 15. Если на обоих входах стробирования уровни логического 0, на том из выходов, номер которого соответствует двоичному эквиваленту входного кода (вход 1 — младший разряд, вход 8 — старший), будет уровень логического 0, на остальных выходах — логической 1. Если хотя бы на одном из входов стробирования Al и А2 уровень логической 1, то независимо от состояний входов на всех выходах ИС формируется логическая ,1,.

Наличие двух входов стробирования существенно расширяет возможности использования ИС. Из двух микросхем К155ИДЗ, дополненных одним ТТЛ-инвертором, можно собрать дешифратор на 32 выхода (рис. 17), дешифратор на 64 выхода собирается из четырех ИС К155ИДЗ и двух инверторов (рис. 18), а на 256 выходов — из 17 ИС К165ИДЗ (рис. 19).

Рис. 16. Выводы ИС К155ИДЗ Рис. 17. Дешифратор на 32 выхода

Интегральная микросхема К155ИД4 (рис. 20) содержит два дешифратора на четыре выхода каждый с объединенными адресными входами и раздельными входами стробирования. Уровень логического 0 на выходах первого (верхнего по схеме) дешифратора формируется (аналогично К155ИДЗ) лишь при наличии на обоих стробирующих входах уровня логического 0. Соответствующим условием для второго дешифратора является наличие на одном из его входов стробирования уровня логической 1 (вывод 1), а на другом — логического 0 (вывод 2). Такая структура ИС позволяет использовать ее в различных вариантах включения. На основе ИС К155ИД4 могут быть построены, в частности, дешифраторы на восемь выходов со входом стробирования (рис. 21) и на 16 выходов (рис. 22). На девяти ИС К155ИД4 можно собрать дешифратор на 64 выхода по схеме, подобный рис. 19.

Практически выходное напряжение ИС К155ИД1 в состоянии 0 может быть несколько выше или ниже порога переключения, поэтому для надежной работы ИС — нагрузки в минусовую цепь питания этой микросхемы следует включить кремниевый диод. Такое включение повысит порог переключения ИС примерно до 2 В, что обеспечит ее согласование с дешифратором К155ИД1. Кроме того, при этом поднимется выходной уровень логического 0 микросхемы примерно до 0,9 В, что вполне достаточно для нормальной работы последующих ИС.

На рис. 27 приведена схема делителя частоты на 10 с переключаемой в пределах 10 — 1,1 скважностью выходных импульсов, иллюстрирующая описанные выше правила согласования дешифратора К.155ИД1 с интегральными микросхемами ТТЛ.

Для коммутации двоичных сигналов используются так называемые мульти-плексеры, представленные в серии К155 интегральными микросхемами К155КП1, К155КП2, К155КП5 и К155КТГ7.

Мультиплексер К165КП7 имеет восемь информационных входов (DO

— D7), три адресных входа (1, 2, 4) и вход стробирования А (рис. 28). У микросхемы два выхода — прямой и инверсный. Если на входе стробирования логическая 1, на прямом выходе 0 независимо от сигналов на других входах. Если на входе стробирования ИС логический 0, сигнал на прямом выходе повторяет сигнал на том входе, номер которого совпадает с двоичным эквивалентом кода на входах 1, 2, 4 мультиплексера. На инверсном выходе сигнал всегда противо-фазен сигналу на прямом выходе.

Наличие входа стробирования позволяет простыми средствами строить мультвплексеры на большее число входов. На рис. 29 приведена схема мультиплексера на 16 входов, на рис. 30 — на 64.

Мультиплексер К155КП5 (рис. 31), в отличие от К155КП7, имеет лишь инверсный выход и не имеет входа стробирования.

Интегральная микросхема К155КП1 (рис. 32) содержит четыре адресных входа 1, 2, 4, S, 16 информационных входов DO

— D15 и вход стробирования А. Выход у этой микросхемы только инверсный. Все свойства и способы включения у нее такие же, как и у К156КП2.

Интегральная микросхема К155КП2 (рис. 33) содержит два мультиплексе ра на четыре информационных входа D0 — D3 с отдельными входами стробирования, объединенными адресными входами и прямыми выходами.

Рис. 27. Делитель частоты на 10 с переключаемой скважностью

Рис. 28. Выводы ИС К155КП7

Рис. 29. Мультиплексер на 16 входов

Рис. 30. Мультиплексер на 64 входа Рис. 31. Выводы ИС К155КП5

Рис. 32. Выводы И С К155КП1 Рис. 33. Схема ИС К155КП2 Рис. 34. Выводы ИС К155ЛП5

Как известно, основная операция, производящаяся в цифровых вычислительных машинах, — сложение. Все другие арифметические операции — вычитание, умножение, деление — сводятся к сложению. Операция сложения двоичных чисел производится с использованием сумматоров и полусумматоров.

В состав серии ИС К155 входят два типа полусумматоров — К155ЛП5 и К155ИП2.

В ИС К155ЛП5 (рис. 34) четыре независимых полусумматора (другие названия — сумматор по модулю два, элемент Исключительное ИЛИ). Каждый из этих элементов работает следующим образом. Если на обоих входах элемента, например 1 и 2, уровень логического 0 — на выходе 3 логический 0. Если на одном из входов логический 0, на другом логическая 1, на выходе — 1,. если на обоих входах — 1, на выходе 0.

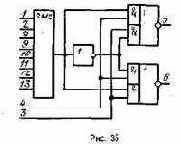

Рис. 35. Схема ИС К155ИП2

В состав ИС КД55ИП2 (рис. 35) входят восьмивходовый сумматор по мо-Дулю 2, обозначенный SM2, инвертор и два логических элемента И — ИЛИ — НЕ;.

Восьмивходовый сумматор по модулю 2 работает аналогично двухвходовому: если на его входах четное число сигналов с уровнем логической 1, на выходе логический 0, если число единиц на входах нечетное, на выходе 1. Остальные элементы ИС позволяют объединять интегральные микросхемы между собой для увеличения числа входов. При подаче уровня логической 1 на вход 3, логического 0 на вход 4, уровень на выходе 5 будет соответствовать выходному уровню сумматора SM2, на выходе 6 — его инверсии.

Бели уровни на (входах 3 и 4 изменить на противоположные, уровни на выходах 5 и 6 также изменятся на противоположные.

Напомним основные свойства двоичных сумматоров. Каждый разряд двоичного сумматора (его иногда называют полным сумматором) имеет три входа — два входа Л и В для слагаемых, вход сигнала переноса от предыдущего разряда С и два выхода — суммы S и сигнала переноса Р в следующий разряд. Работа сумматора иллюстрируется табл. 3. Входы А, В, С, вообще говоря, равноправны. Сигнал суммы S принимает значение логической ,1 при нечетном числе единиц на входах А, В и С и логического 0 при четном, как и в рассмотренных выше полусумматорах. Сигнал переноса Р равен логической 1 при числе единиц на входах, равном 2 или 3. Интересным свойством табл. 3 является ее симметрия: замена 0 на 1 и наоборот не нарушает ее истинности. Это свойство используется для упрощения схем сумматоров.

Таблица 3

|

Входы |

Выходы |

Входы |

Выходы |

||||||

|

Л |

в |

с |

S |

р |

А |

в |

с |

S |

р |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Если на всех входах сигналы отсутствуют (А = В = С = 0), выходные сигналы также отсутствуют: S = 0, Р=0 (Р=0).

Входные сигналы А и В могут быть поданы не только в прямом коде (входы 8 и 9 для А, 12 и 13 для В), но и в инверсном (входы 11 для А и 2 для В). При использовании инверсных входных сигналов входы 8, 9, 12 и 13 следует соединить с общим проводом, а при использовании прямых сигналов — попарно соединить выводы 10 и 11, 1 и 2.

Элементы DD1 и DD2 микросхемы имеют открытый коллекторный выход, поэтому выводы 10 и 1 могут использоваться или как выходы элементов DD1 и DD2, или как входы, превращающие элементы DD1 и DD2 типа И — НЕ в элементы И — ИЛИ — НЕ подключением к этим выводам выходов ИС К155ЛА8. В любом случае использования выводов 10 и 1 между ними и плюсом питания необходимо включать резисторы 1 — 2 кОм.

Рис. 36. Схема ИС К155ИМ1

Рис. 37. Схема соединения интегральных микросхем К155ИМ1 в двухразрядный сумматор

Рис. 38. Выводы ИС К155ИМ2 Рис. 39. Выводы ИС К155ИМЗ

При соединении ИС К155ИМ1 в многоразрядный сумматор (рис. 37) используется описанное выше свойство симметрии полного сумматора относительно замены входных и выходных сигналов инверсными. В первом разряде входные сигналы подаются на прямые входы ИС DD1, выходной сигнал суммы снимается с прямого выхода S, сигнал переноса — с единственного (инверсного) выхода Р. На второй разряд сумматора входные сигналы А и В подаются на инверсные входы, на прямой вход С подается инверсный сигнал переноса с первого разряда, выходной прямой сигнал суммы формируется на инверсном выходе 5, выходной прямой сигнал переноса — на инверсном выходе Р. Третий разряд сумматора работает так же, как и первый, четвертый — как второй и т. д.

Такое чередование режима работы одноразрядных сумматоров обеспечивает минимальную задержку распространения сигнала в самой длинной цепи — в цепи формирования сигнала переноса.

Интегральная микросхема К155ИМ2 (ряс. 38) представляет собой объединение двух микросхем К155ИМ1, соединенных в соответствии с рис. 37 с исключенными неиспользуемыми инверторами. Интегральная микросхема К155ИМЗ (рис. 39) соответствует двум микросхемам К155ИМ2, в которых вы-:ход переноса первой ИС соединен со входом С второй.

ЭЛЕКТРОННЫЕ ЧАСЫ

Описанные выше электронные часы на

Описанные выше электронные часы на интегральных микросхемах серии К.155 потребляют от источника питания +5 В ток 0,4 — 0,8 А в зависимости от типа использованных индикаторов. Питание таких часов необходимо осуществлять от сети через понижающий трансформатор, выпрямитель и стабилизатор напряжения, в результате чего часы получаются довольно громоздкими.

Применив интегральные микросхемы серии К134, можно построить электронные часы с бестрансформаторным питанием. Интегральные микросхемы серии К134 отличаются от ИС серии К155 прежде всего значительно меньшей потребляемой мощностью, типом корпуса, наличием ИС, содержащих два JK-триг-гера в одном корпусе. В серии К134, однако, нет дешифратора с высоковольтным выходом, поэтому в часах использованы интегральные микросхемы К133ИД1, совпадающие по характеристикам с ИС КГ55ИД1. Корпус ИС К133ИД1 — плоский, с пленарными выводами, по конструкции близок к корпусу ИС серии К134.

Часы на ИС серии К134 потребляют по цепи +5 В ток около 100 мА. В часах применен делитель частоты кварцевого генератора с переключаемым коэффициентом деления, что позволяет применять в них кварцевый резонатор с любой частотой в пределах от 50 до 559,24 кГц.

Принципиальная схема часов приведена на рис. 48. На ИС DD1 собран кварцевый генератор с резонатором Z1. Импульсы с выхода генератора поступают на делитель с коэффициентом пересчета 4 (ИС DD3) и далее на делитель с переключаемым коэффициентом деления (ИС DD4 — DD14).

Этот делитель работает по принципу предварительной записи в счетчик числа, на которое нужно уменьшить коэффициент пересчета (см. с. 9). В таком делителе часть триггеров устанавливается при переполнении счетчика в 0, а часть — в 1. В результате переполнение счетчика происходит не после поступления 2™ импульсов делителя (n — число триггеров делителя), а ранее. В момент переключения последнего триггера в нулевое состояние вновь производится установка части триггеров в 0, части — в 1.

Таким образом, коэффици ент пересчета делителя уменьшается относительно 2n на число, записываемое в делитель при сбросе.

Триггеры К134ТВ14 имеют лишь входы установки в 0. Поэтому структура делителя по сравнению с описанной выше несколько изменена — триггеры DD10 — DD14 делителя устанавливаются в 0, а сигналы на следующие за ними триггеры подаются либо с прямого, либо с инверсного выхода. Это эквивалентно установке триггеров соответственно в 0 и 1.

Входы триггеров DD4 — DD9, DD10.1 подключены к инверсным выходам предыдущих триггеров, в результате чего их частичная установка в 0 также эквивалентна записи в делитель некоторого числа. Ошибка, возникающая вследствие невозможности установки части триггеров DD4 — DD9 в необходимое состояние, не превышает 0,1 с и существует лишь в момент пуска часов, на коэффициенте пересчета делителя она не сказывается,

Запись необходимого числа в делитель в момент переключения триггера осуществляется с помощью дифференцирующей цепочки C3R4R5 и элементов DD2.3 и DD2.4.

Делитель DD4 — DD14 настраивают так, чтобы на его выходе формировался один импульс в минуту. Импульсы с выхода делителя поступают на вход счетчика единиц минут DD1S — DD16 и далее на счетчики десятков минут DD17 — DD18, единиц часов DD19 — DD20, десятков часов DD21. Коэффициент пересчета счетчика часов, равный 24, реализован с помощью схемы сброса на элементах DD22.1, DD22.2, DD22.3. Состояние счетчиков дешифрируется микросхемами DD23 — DD26 и индицируется газоразрядными индикаторами HG1 — HG4.

В связи с тем что используемые JK-триггеры имеют по одному входу 1 и К, декады часов собраны по схеме, отличающейся от приведенных ранее. Код работы таких декад невесовой, он приводится к коду 1 — 2 — 4 — 8 с помощью диодов VD4 — VD7.

Для питания часов применен бестрансформаторный источник питания. Напряжение сети гасится на конденсаторах С4 и С5, выпрямляется мостом VD2 и стабилизируется стабилитроном VD3. Пульсации напряжения на VD3 сглаживаются конденсатором Сб. Величина пульсации составляет около 500 мВ от пика до пика, но это допустимо для ИС ТТЛ.

Напряжение питания на аноды ламп HG1 — HG4 подается с однополупе-риодного выпрямителя на диоде VD1 через токоограничительные резисторы R8-R11.

Установка показаний часов возможна лишь в моменты, соответствующие целым часам. Порядок установки следующий. Нажимают кнопку SB1, при этом триггер на элементах DD2.1 и DD2.2, необходимый для подавления дребезга контактов кнопки (ом. с. 26), переключается в такое состояние, при котором на выходе элемента DD2.1 формируется уровень логического 0. Этот сигнал устанавливает триггеры делителя и счетчиков минут в нулевое состояние, а также вызывает появление на входе первого триггера счетчика часов DD19.1 логической 1. В момент отпускания кнопки сигнал на входе DD19.1 изменяется с логической 1 на логический 0, в результате чего к показаниям счетчика часов прибавляется единица. Нажимая необходимое число раз кнопку SB1, можно установить необходимое показание часов. Последний раз отпустить кнопку необходимо по шестому сигналу поверки времени.

Рис. 48. Схема электронных часов на МС серии К134

Коррекция показаний часов в процессе эксплуатации производится однократным нажатием кнопки по первому и отпусканием по шестому сигналу. Если часы ушли вперед более чем на 5 с, кнопку следует нажать ранее, чем они переключатся самостоятельно, и отпустить, как обычно, по шестому сигналу.

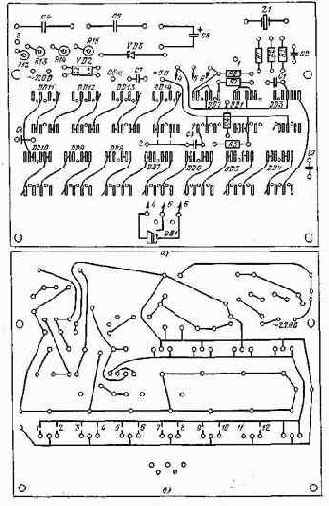

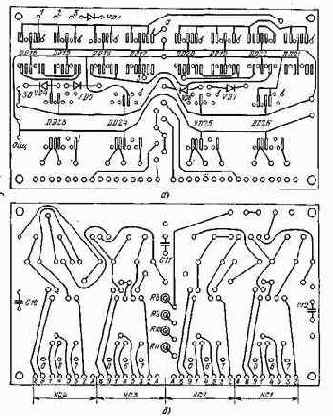

Часы собраны на двух печатных платах разного размера 75X95 мм (рис. 49) и 55x95 мм (рис. 50). В часах использованы резисторы МТ, конденсаторы К73-17 (С4, С5), К50-6 (С6), К10-17 (остальные). На плате меньшего размера детали установлены с двух сторон, их расположение показано на чертежах печатных плат. Вариант конструктивного оформления часов показан на рис. 51. Корпус оклеен из прозрачного органического стекла толщиной 3 ш и оклеен светлой декоративной пленкой под дерево. Торцевая и внутренняя поверхности верхней, нижней и боковых стенок корпуса окрашены темной коричневой нитроэмалью. В планке на передней стенке корпуса после ее наклейки лезвием бритвы вырезано окно против индикаторов.

Платы и задняя стенка крепятся винтами М2 к четырем бобышкам из органического стекла, приклеенным к боковым стенкам корпуса.

В качестве кнопки SB1 использован микропереключатель МПЗ-,1, закрепленный на плате большего размера. Для нажатия на шток переключателя в нижней стенке часов напротив него просверлено отверстие 0 1,8 мм. Нажи- -мают на шток при пуске часов отрезком проволоки, например разогнутой кан- целярской скрепкой.

Платы соединяют между собой пятью проводниками, соответствующие контактные площадки на платах помечены +5 В, Общ., 1, 2, 3.

Настройку делителя частоты под конкретный кварцевый резонатор производят следующим образом. Частоту кварцевого резонатора делят на 4 (что соответствует делению в триггерах DD3.1 и DD3.2) и умножают на 60. В результате получается необходимый коэффициент деления. Его уменьшают на единицу и переводят в двоичную форму.

Рассмотрим в качестве примера настройку делителя под кварцевцй резонатор с частотой 100 кГц. Необходимый коэффициент деления 100 000:4X60 = 1500 000. Двоичный эквивалент числа 1 499 99910 равен 1 0110 1110 0011 0101 1111 г. Число знаков в двоичном эквиваленте определяет число необходимых триггеров, в данном случае 21, поэтому триггер DD14.2 не используется и сигнал на конденсатор СЗ снимается с прямого выхода 9 триггера DD14.1.

Если необходимое число триггеров составляет 22 (частота кварцевого резонатора находится в пределах от 139 810 до 279 620 Гц), сигнал снимается с вывода 12 DD14.2.

Рис. 49. Печатная плата электронных часов большая

Двенадцать младших разрядов двоичного эквивалента определяют подключение входов R микросхем DD4 — DD9 к шине установки нуля — если в соответствуюшгм разряде 0, вход R подключают к шине с помощью перемычки, если 1 — оставляют свободным. В данном случае 0 в 6, 8, 11 и 12 разрядах (начиная с младшего), следовательно, к шине установки нуля подключают входы R триггеров DD6.2, DD7.2, DD9.1, DD9.2 (счет начинается с триггера DD4.1, на триггеры DD3 установка 0 никогда не подводится).

Остальные раз ряды двоичного эквивалента определяют, какие входы (прямые или инверсные) триггеров DD10 — DD14 необходимо подключать ко входам следующих триггеров. Если в двоичном эквиваленте в соответствующем разряде 0, вход следующего триггера подключается к инверсному выходу данного триггера (вывод 8 или 13), если 1 — к прямому (вывод 9 или 12). Неиспользуемый вывод триггера не подпаивается к контактной площадке, его оставляют свободным или обламывают. Так как в старшем разряде двоичного эквивалента всегда стоит 1, с последнего триггера выходной сигнал всегда снимается с прямого выхода.

Рис. 50. Печатная плата электронных часов малая

В данном случае ко входам следующих триггеров подключаются выводы 8 и 12 микросхемы DD10, 9 и 12 DD11, 8 и 12 DD12, 9 я 13 DD13, выходной сигнал снимается с вывода 9 DD14.

Рис. 51. Конструкция электронных часов

После установки теплового режима в корпусе часов проверяется уход показаний за 3 — 4 недели и уточняется настройка делителя. Предположим, часы спешат на 2 с в сутки. В этом случае коэффициент деления нужно увеличить на (2*1600 000)/86400 = 35 (86 400 — число секунд в сутках). Таким образом, необходимый коэффициент деления составит 1 500 035, его уменьшают на единицу и по нему вновь определяют двоичный эквивалент и рассчитывают установку перемычек (распайка выводов триггеров DD10 — DD14, как правило, не меняется).

При применении в часах кварцевого резонатора с частотой менее 69905 Гц микросхему DD3 не устанавливают, ее контактные площадки 1 и 8 соединяют между собой проволочной перемычкой, а частоту кварцевого резонатора при определении коэффициента деления на 4 не делят.

Если же частота кварцевого резонатора превышает 279 620 Гц, но менее 559 240 Гц, выход делителя (точка 2 платы большего размера) подключают ко входу 1 DD17 (точка а), выход 13 DD17 (точка б) подключают к точке 2 платы меньшего размера. При этом при расчете коэффициента деления частоты кварцевого резонатора делят не на 4, а на 8.

При налаживании часов следует помнить, что к включенным в сеть часам нельзя подключать приборы с металлическим корпусом, можно только логические щупы (питание на них можно взять со стабилитрона VD2) и авометры. Если для поиска неисправности или измерения частоты кварцевого резонатора необходимо подключение осциллографа или частотомера, питание на часы следует подать от источника постоянного напряжения 15 — 18 В, замкнув выводы конденсаторов С4 — С5 между собой.

Для облегчения теплового режима часов целесообразно резисторы R13 — R15 в часы не устанавливать, на их место установить перемычку, а в сетевую вилку в разрыв одного из проводов включить проволочный резистор 51 — 75 Ом.

При правильной настройке делителя месячная ошибка в ходе часов не превышает 5 с.

БУДИЛЬНИКИ И ТАЙМЕРЫ

Первой конструкцией на цифровых ИС,

Первой конструкцией на цифровых ИС, изготовляемой радиолюбителями, являются, как правило, электронные часы. На ИС серии К155 можно собрать часы, самые разнообразные по своим схемам. Одна из самых простых схем приведена на рис. 40.

Часы включают в себя кварцевый генератор на ИС DD1 и кварцевом резонаторе Z1 на частоту 100 кГц, делитель частоты с коэффициентом деления 10s (DD2 — DD6), счетчики секунд (DD7, DD8), минут (DD9, DD10) и часов (DD11 — DD12), а также не показанные на рис. 40 дешифраторы и индикаторы. Интегральные микросхемы DD7, DD9, DD11 (К155ИЕ2) имеют коэффициент пересчета 10, а в ИС DD8 и DD10 (К155ИЕ4) для получения коэффициента деления 6 используются лишь первые три триггера, что обеспечивает необходимый для дешифраторов код 1 — 2 — 4.

Для пересчета на 24 в счетчике часов выходы 8 микросхем DD11 и DD12 подключены ко входам Л этих же микросхем. При достижении состояния 4 ИС DD11 и состояния 2 ИС DD12 на обоих входах R этих счетчиков формируется уровень логической 1, и они переходят в нулевое состояние.

Выходы счетчиков секунд, минут и часов подключены ко входам дешифраторов, выходы дешифраторов — к соответствующим электродам индикаторов. В часах могут быть использованы самые разнообразные индикаторы и соответствующие им дешифраторы.

Эффектно выглядят электронные часы, если индикация секунд производится на индикаторах меньшего размера, чем индикация часов и минут. В этом случае индикаторы секунд меньше раздражают глаза своим постоянным; переключением. Хорошо смотрятся часы с газоразрядными индикаторами часов и минут и небольшими полупроводниковыми индикаторами секунд красного свечения, установленными между индикаторами часов и минут.

Подключение газоразрядных индикаторов с помощью дешифратора К155ИД1 описано выше. Для подключения полупроводниковых семисегментных индикаторов могут использоваться интегральные микросхемы преобразователей кода 1 — 2 — 4 — 8 в код семисегментного индикатора К514ИД1 и К514ИД2.

Цоколевжа этих микросхем одинакова (рис. 41).

Рис. 40. Схема электронных часов на ИС серия К155

Интегральная микросхема К514ИД1 служит для подключения индикаторов с общим катодом и содержит ограничительные резисторы, обеспечивающие выходной ток около 5 мА. Электроды индикатора, рассчитанного на указанный ток, подключают к выходам микросхемы, а общий катод соединяют с общим проводом.

Рис. 41. Выводы ИС К514ИД1 и К514ИД2

Интегральная микросхема К514ИД2 не содержит ограничительных резисторов, ее выходы через внешние резисторы подключают к катодам индикаторов с общим анодом. Сопротивление резисторов выбирают, исходя из номинального тока индикаторов (максимально допустимый ток для ИС 20 мА). Общий анод подключают к источнику постоянного или пульсирующего напряжения, не превышающего 6 В.

Вход 5 микросхем К514ИД1 и К514ИД2 служит для гашения индикации при подаче на него логического 0. Интегральные микросхемы К.514ИД2 могут быть использованы для накаль-ных индикаторов, их включают без ограничительных резисторов. Общий вывод индикаторов подключают к плюсу источника постоянного или пульсирующего напряжения, соответствующего их рабочему напряжению питания.

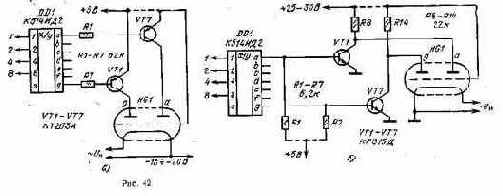

Люминесцентные вакуумные индикаторы можно подключить к выходам микросхемы К514ИД2 с использованием р — n — р-транзисторов с допустимым напряжением коллектор — эмиттер не менее 30 В в соответствии с рис. 42,а. Подключение возможно и с использованием n — р — n-транзисторов в соответствии с рис. 42,6.

Интегральная микросхема К514ИД1 может быть использована для подключения к вакуумным люминесцентным индикаторам по схеме рис. 43.

Установка начальных показаний (сверка) часов производится с использованием эталонных часов следующим образом. Нажав на кнопку SB3, подают на вход счетчика секунд импульсы с частотой 5000 Гц и устанавливают показания счетчика часов. Затем, нажав на кнопку SB2, подают на вход счетчика секунд импульсы с частотой 100 Гц и устанавливают показания счетчика минут.

Наконец, нажав кнопку SB1, отпускают ее в момент, когда секундная стрелка эталонных часов покажет на циферблате на число (12.

Можно исключить из часов кнопку SB2, в этом случае входы R DD9 и DD10 следует соединить с аналогичными входа!ми DD2 — DD8, а сверку часов можно будет производить лишь в моменты времени, соответствующие целым часам.

Использованный в часах метод пуска обладает тем недостатком, что установка часов, минут и секунд взаимосвязана и должна производиться обязательно в указанном порядке. В то же время метод наиболее прост, так как не требует специальных мер по борьбе с так называемым дребезгом — многократным неконтролируемым замыканием и размыканием механических контактов, кнопок, переключателей, реле и т. п., в результате которого вместо одного импульса включения формируется «пачка» импульсов.

Какие изменения в схеме часов можно сделать при отсутствии тех или иных микросхем?

Рис. 42. Подключение вакуумных люминесцентных индикаторов к ИС К514ИД2

Рис. 43. Подключение вакуумных люминесцентных индикаторов к ИС К514ИД1

Рис. 44. Делитель на 6 на ЛК-триггерах {а) и D-триггерах (б)

Интегральные микросхемы К155ИЕ1 можно заменить на К.155ИЕ2. При отсутствии микросхем К155ИЕ2, К.155ИЕ4, К155ИЕ5 на место микросхем DD2 — DD7, DD9, DD11 можно установить декады по схемам рис. А,а или 5,а. К декаде по рис. Ъ,а интегральные микросхемы К15ШД1, К514ИД1, К514ИД2 следует подключать по схеме рис. 26. Делители частоты на 6 можно выполнить по схемам рис. 44,а и б соответственно на JK- или D-триггерах. Дешифратор к делителю по рис. 44,6 следует подключать по схеме рис. 45.

Рис. 45. Подключение дешифратора к делителю на 6 по схеме рис. 44.6

Счетчик часов с коэффициентом пересчета 24 можно собрать по схемам рис. 46. На рис. 46,а знаком СТ10 помечена декада по схеме рис. 4,а, на рис. 46,6 — по схеме рис. Ъ,а. В случае применения декад и счетчиков на микросхемах КД55ТВ1 или К155ТМ2 следует использовать кнопку SB1 с нормально разомкнутыми контактами.

Рис. 46. Схема счетчика часов на JK-триггерах (а) и D-триггерах (б). Прямой выход DD2 (рис. 46,а) соединить с выходом 2 счетчика

При отсутствии кварцевого резонатора на частоту 100 кГц можно использовать кварцевые резонаторы на другие частоты. Если частота резонатора в 2 — 10, 12 или 16 раз превышает частоту 100 кГц, между выходом генератора и входом DD2 следует включить одну из ИС (К165ИЕ2, К156ИЕ4, К155ИЕ5), соединив ее выводы для получения необходимого коэффициента деления в соответствии с табл. 2.

Если значение частоты кварцевого резонатора в герцах допускает разложение на указанные выше множители, можно установить несколько микросхем с различными коэффициентами деления для получения результирующей частоты 1 Гц. При этом для подачи на кнопки SB2 и SB3 сигналов с частотами 60 — 120 Гц и 3600 — 7200 Гц с выходов делителя необходимо сделать соответствующие отводы.

Более экономичным по структуре получается построение делителя с произвольным коэффициентом деления по схеме рис. 47. Делитель содержит цепочку ИС К155ИЕ5 DD1 — DD3 и элемент И (DD4 — DD6) с большим числом входов, выход которого подключен ко входам R интегральных микросхем цепочки. Входы элемента И подключены к определенным выходам цепочки, это подключение и определяет коэффициент пересчета.

Делитель работает по принципу принудительной установки в 0 при достижении требуемого состояния (см. с. 9).

Для определения количества ИС К155ИЕ5 в делителе, количества входов элемента И и порядка подключения входов этого элемента к выходам ИС не- . обходимый коэффициент пересчета переводят в двоичную форму.

Для перевода числа в двоичную форму его делят на 2, остаток (0 или 1) записывают. Результат вновь делят на 2, остаток снова записывают и так далее, пока после деления не останется нуль. Первый остаток является младшим разрядом двоичной формы числа, последний — старшим.

Число разрядов получившегося двоичного числа определяет необходимое «число триггеров цепочки делителя, число единиц в двоичной форме числа равно числу входов в элементе И.

Расстановка единиц в двоичном эквиваленте определяет, к каким выходам цепочки необходимо подключить входы элемента И. Наличие 1 в младшем разряде означает подключение к выходу 1 цепочки, в следующем — к выходу 2 и т. д.

Для примера рассмотрим расчет для кварцевого резонатора с частотой 150007 Гц. Двоичный эквивалент числа 150 0074о составляет 10 0100 1001 1111 011Ь. В двоичном эквиваленте 18 разрядов, необходимая длина цепочки — 18 триггеров или 5 микросхем К155ИЕ5. Число единиц в двоичном эквиваленте — 1.1, следовательно, необходим элемент И на 11 входов. Входы элемента И необходимо подключить к следующим выходам цепочки: 1, 2, 3, 5, 6, 7, 8, 9, 12, 15, 18. Выходной сигнал снимается с выхода 18 цепочки — последнего, подключаемого ко входу элемента И. В цепочке возможно применение интегральных микросхем К155ИЕ2, в этом случае расчет упрощается, но число ИС в цепочке увеличивается.

Рис. 47. Схема делителя частоты с переключаемым коэффициентом деления

Из-за накопления задержек в цепочке для нормальной работы делителя необходимо, чтобы частота входных импульсов не превышала 1 МГц. Если частота кварцевого генератора более 1 МГц, необходимо поделить ее до частоты 500 кГц — 1 МГц с помощью одной микросхемы К155ИЕ5 и лишь потом подать на делитель.

Делитель с произвольным коэффициентом деления на ИС К155ТВ1 или К155ТМ2 также можно собрать по схеме рис. 47, но в этом случае более экономичным по количеству микросхем является способ, который приведен ниже при описании электронных часов на интегральных микросхемах серии KI34.

Точная подстройка кварцевого генератора может быть обеспечена включением последовательно с кварцевым резонатором конденсатора емкостью от единиц до сотен микофарад, а также подбором емкости: СЗ (см. рис. 40).

ОБЩИЕ СВЕДЕНИЯ

Отечественная промышленность выпускает обширную номенклатуру интегральных микросхем (ИС). Широкое применение для построения устройств автоматики и вычислительной техники находят цифровые ИС серии К155, которые изготовляются по стандартной технологии биполярных ИС транзистор-но-транввстарной логики (ТТЛ). Номенклатура ИС серии КШ5 составляет около 100 наименований.

Все ИС серии КД55 имеют напряжение питания 5 В±5%. Интегральные микросхемы выпускаются в пластмассовых корпусах трех типов, отличающихся количеством выводов (14, 16, 24) и размерами, и имеют диапазон рабочих температур от — 10 до +70° С. Часть микросхем выпускается также в керамических корпусах и имеет обозначение К.М155. Температурный диапазон микросхем в керамических корпусах — от — 45 до +85° С.

Интегральные микросхемы серии К155 имеют выходной уровень логического 0 не более 0,4 В (типовое значение 0,1 — 0,2 В), выходной.уровень логической 1 не менее 2,4 В (типовое значение 3,2 — 3,5 В), типовую нагрузочную способность — 10.

В табл. 1 приведены значения потребляемой мощности, предельной частоты тактовых импульсов, а также число выводов корпуса и разводка выводов питания рассматриваемых ниже микросхем.

При проектировании цифровых приборов следует иметь в виду, что фактическое быстродействие триггеров и счетчиков превышает указанное в табл. 1 в 1,5 — 2 раза, а потребляемая мощность в среднем в 1,5 — 2 раза меньше предельной, указанной в таблице.

При разработке принципиальных схем различных устройств всегда возникает вопрос: что делать с неиспользуемыми входами интегральных микросхем. Для ИС ТТЛ, к которым относятся ИС серии К155, возможно несколько вариантов. Во-первых, неиспользуемые входы микросхем можно никуда не подключать [Для ИС некоторых серий (К533, К555, К530, К531 и др.) оставлять входы неподключенными не допускается.], т. е. подпаивать к контактной площадке минимальных размеров, к которой (это важно) не подключены проводники.

При таком варианте несколько уменьшается быстродействие микросхем. Во-вторых, возможно подключение неиспользуемых входов к используемым входам того же элемента, но это несколько увеличивает нагрузку (в основном емкостную) на микросхему — источник сигнала, что также снижает быстродействие. Неиспользуемые входы J триггеров можно подключать к инверсным выходам тех же триггеров, а К — к прямым. Это очень удобно, так как указанные выводы триггеров обычно расположены рядом. Можно подключать неиспользуемые 1входы к выходу неиспользуемого элемента И — НЕ, входы которого при этом надо соединить с общим проводом. Наконец, можно объединять неиспользуемые входы ИС и подключать их к источнику питания +5 В через резистор 1 кОм (до 20 входов к одному резистору). Последние два способа не снижают быстродействия ИС.

Таблица 1

|

Обозначение, ИС |

Потребляемая мощность, мВт |

Предельная частота, МГц |

Число выводов корпуса |

Выводы питания |

|

|

+ 5 В |

Общ. |

||||

|

К155ТВ1 |

105 |

10 |

14 |

14 |

7 |

|

К155ТМ2 |

157,5 |

10 |

14 |

14 |

7 |

|

К155ТМ5 |

265 |

— |

14 |

4 |

11 |

|

К155ТМ7 |

265 |

— |

16 |

5 |

12 |

|

К155ИЕ1 |

150 |

10 |

14 |

14 |

7 |

|

К155ИЕ2 |

265 |

10 |

14 |

5 |

10 |

|

К155ИЕ4 |

255 |

10 |

14 |

5 |

10 |

|

К155ИЕ5 |

265 |

10 |

14 |

5 |

10 |

|

К155ИЕ6 |

510 |

15 |

16 |

16 |

8 |

|

К155ИЕ7 |

510 |

15 |

16 |

16 |

8 |

|

К155ИЕ8 |

600 |

15 |

16 |

16 |

8 |

|

К155ИР1 |

410 |

10 |

14 |

14 |

7 |

|

К155ИД1 |

132 |

— |

16 |

5 |

12 |

|

К155ИДЗ |

250 |

— |

24 |

24 |

12 |

|

К155ИД4 |

210 |

— |

16 |

16 |

8 |

|

К155КП1 |

360 |

— |

24 |

24 |

12 |

|

К155КП2 |

315 |

— |

16 |

16 |

8 |

|

К165КП5 |

230 |

— |

14 |

14 |

7 |

|

К155КП7 |

260 |

— |

16 |

16 |

8 |

|

К155ЛП5 |

262,5 |

— |

14 |

14 |

7 |

|

К155ИП2 |

294 |

— |

14 |

14 |

7 |

|

К155ИМ1 |

175 |

|

14 |

14 |

7 |

|

К155ИМ2 |

290 |

|

14 |

4 |

11 |

|

К155ИМЗ |

640 |

— |

16 |

5 |

12 |

Недопустимо подключать ко входу ИС проводник, который во время работы может оказаться неподключенным к выходу источника сигнала, например, при управлении от кнопки или переключателя. Такие проводники обязательно следует подключать к источнику +6 В через резистор 1 — .1(0 кОм.

На печатных платах с использованием ИС серии К155 необходима установка блокировочных конденсаторов между цепью +5 В и общим проводом. Их количество определяется одним-двумя конденсаторами емкостью 0,033 — 0,047 мкФ на каждые десять микросхем. Конденсаторы следует располагать на плате по возможности равномерно. Их следует также установить рядом со всеми ИС с мощным выходом (например, К155ЛА6) или с потребляемой мощностью более 0,5 Вт.

Цифровые ИС по своим функциям делятся на два широких класса — комбинационные и последовательностные. К первому классу относятся ИС, не имеющие внутренней памяти, состояние выходов этих ИС однозначно определяется уровнями входных сигналов в данный момент времени.

Ко второму классу относятся ИС, состояние выходов которых определяется не только уровнями входных сигналов в данный момент времени, но и состоянием ИС в предыдущий момент из-за наличия внутренней памяти.

К комбинационным ИС серии К155 относятся простые логические элементы И — НЕ, И — ИЛИ — НЕ, НЕ, ИЛИ — НЕ, И, ИЛИ, имеющие в своем обозначении буквы ЛА (К155ЛАЗ), ЛР (К155ЛР1), ЛН (К155ЛН1), ЛЕ (К155ЛЕ1), ЛИ (К155ЛИ1), ЛЛ (К155ЛЛ1), более сложные элементы — дешифраторы (К155ИД1, К155ИДЗ, КИ55ИД4), мультиплексеры (К155КП1, К155КП2, К155КП5, К.155КП7), сумматоры по модулю 2 (К155ЛП5, К155ИП2), полные сумматоры (КЛ55ИМ1, К155ИМ2, К155ИМЗ), а также некоторые другие.

К последовательностным ИС относятся триггеры (К155ТВ1, К155ТМ2, К155ТМ5, К155ТМ7), счетчики (К155ИЕ1 — К155ИЕ8), сдвигающие регистры (К155ИР1) и др.

Работа логических элементов достаточно проста — для элементов И выходной уровень логической 1 формируется при подаче на все входы элемента уровней логической 1, для элемента ИЛИ для формирования уровня логической 1 на выходе достаточно подачи хотя бы на один вход уровня логической 1.Элементы И — НЕ (основной элемент серии К155) и ИЛИ — НЕ дополнительно инвертируют выходной сигнал, элемент И — ИЛИ — НЕ состоит из нескольких элементов И, выходы которых подключены ко входам элемента ИЛИ — НЕ.